Description

Overview

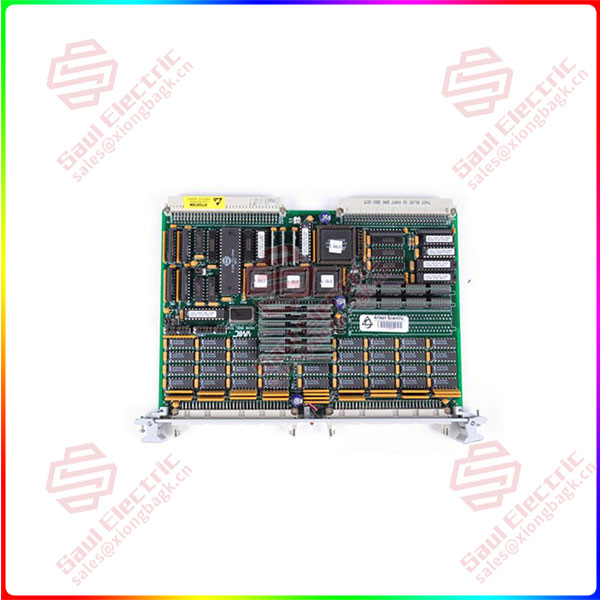

Essential details:VMIVME-5576 Fiber-Optic Reflective Memory with Interrupts

- High-Speed Fiber Optic Network

- 2000 m Between Nodes, Up to 256 Nodes

- Error Detection

- Redundant Transmission Mode for Suppressing Errors

- A24:A32:D32:D16:D8 Memory Access

The VMIC / GE Fanuc VMIVME-5576 Reflective Memory interface allows data to be shared between up to 256 independent systems (nodes) at rates up to 6.2 Mbyte/s. Each Reflective Memory board may be configured with 256 Kbyte to 1 Mbyte of on-board SRAM. The local SRAM provides fast Read access times to stored data. Writes are stored in local SRAM and broadcast over a high-speed fiber-optic data path to other Reflective Memory nodes. The transfer of data between nodes is software transparent, so no I/O overhead is required. Transmit and Receive FIFOs buffer data during peak data rates to optimize CPU and bus performance to maintain high data throughput.

The Reflective Memory also allows interrupts to one or more nodes by writing to a byte register. These interrupt (three level, user definable) signals may be used to synchronize a system process, or used to follow any data that may have preceded it. The interrupt always follows the data to ensure the reception of the data before the interrupt is acknowledged. The VMIVME-5576 requires no initialization unless interrupts are being used. If interrupts are used, vectors and interrupt levels must be written to on-board registers and the interrupts armed.

Each node on the system has a unique identification number between 0 and 255. The node number is established during hardware system integration by placement of jumpers on the board. This node number can be read by software by accessing an on-board register. In some applications, this node number would be useful in establishing the function of the node.

VMIVME-5550

lf you need to inquire or purchase ,please send the product models to my email or call medirectly .

sunny He

[Email] sales@saulcontrol.com

[Mobile] 86-18059884797

[WhatsApp] 86-18059884797

[Skype] sales@saulcontrol.com

VMIVME-5576 Fiber-Optic Reflective Memory with Interrupts

This module is one of the VMIC/GE Fanuc modules, designated as the VMIVME-5576 unit of the series. This board is designed to function as a Reflective Memory board, able to transfer data. It does so by recording it onto on-board RAM. The Reflective Memory concept for these boards provides a very fast and efficient way of sharing data across distributed computer systems.

The VMIC/GE Fanuc series was developed by General Electric and produced by the company’s industrial automation division, but these products were later purchased and developed by Abaco Systems.

The VMIVMVE-5576 interface module permits data to be shared between 256 independent systems at a rate of up to 6.2 MB.

The Reflective Memory boards within the VMIC/GE Fanuc line are designed to be configurable for the data shared and retained, with up to 256 KB to 1 MB of onboard SRAM.

The reflective memory that is integrated into these VMIC/GE Fanuc models is programmed to interrupt several nodes at once by sending it to a byte register. These signals synchronize a system process.

The node interrupt is able to follow the data. This ensures that the data reception is completed, and then enables the interrupt after the reception. The VMIVME-5576 unit is built so that no initialization is needed before the interrupt capabilities are used.

1 Year Warranty

1 Year Warranty