Description

Overview

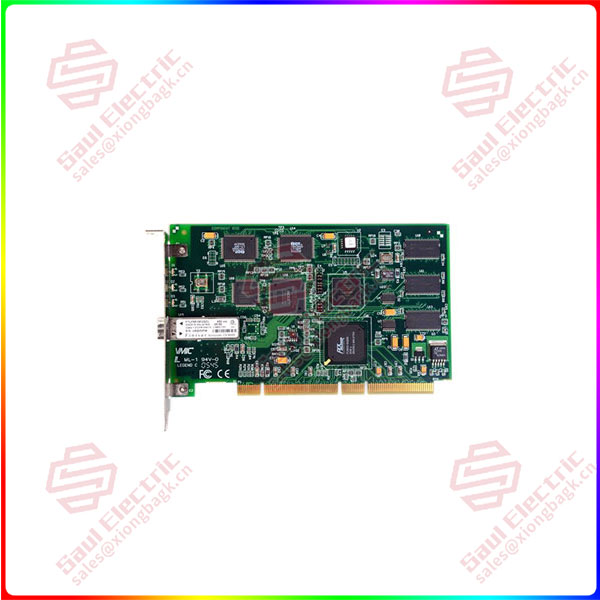

Essential details:VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

Introduction: VMIPCI-5565 is the PCI member of the GE Fanuc Embedded Systems’ VMIxxx-5565 family of Reflective Memory (RFM) real time network products. The other members of the family are VMIVME-5565, VME-compatible board, and VMIPMC-5565, the PCI mezzanine card (PMC). All three of these products are network compatible, and may be integrated into a network in any combination.

This family of products allows computers, workstations, PLCs, and other embedded controllers with dissimilar operating systems or no operating system at all to share data in real time.

To the local node, the Reflective Memory board appears as shared memory. Data can be written to or read from the memory by any level of software, including the application itself.

Data written to the Reflective Memory in one node is transported by the network hardware to all other nodes and placed in the same address on those node’s Reflective Memory boards. This transport of data is accomplished without the involvement of the processors on any node. By this system, all nodes on the network have a local copy of shared data available for immediate access.

Product Overview: The Reflective Memory concept provides a very fast and efficient way of sharing data across distributed computer systems.

The VMIPCI-5565 Reflective Memory interface allows data to be shared between up to 256 independent systems (nodes) at rates up to 174MB/s. Each Reflective Memory board may be configured with 64MB or 128MB of onboard SDRAM. The local SDRAM provides fast Read access times to stored data. Writes are stored in local SDRAM and broadcast over a high speed

fiber-optic data path to other Reflective Memory nodes. The transfer of data between nodes is software transparent, so no I/O overhead is required. Transmit and Receive FIFOs buffer data during peak data rates to optimize the host computer and bus performance to maintain high data throughput.

The Reflective Memory also allows interrupts to one or more nodes by writing to a byte register. These interrupt (four levels, each user definable) signals may be used to synchronize a system process, or used to follow any data. The interrupt always follows the data to ensure the reception of the data before the interrupt is acknowledged.

Each node on the system has a unique identification number between 0 and 255. The node number is established during hardware system integration by placement of jumpers on the board. This node number can be read by software by accessing an onboard register. In some applications, this node number would be useful in establishing the function of the node.

VMIPCI-5565

lf you need to inquire or purchase ,please send the product models to my email or call medirectly .

sunny He

[Email] sales@xiongbagk.cn

[Mobile] 86-18059884797

[WhatsApp] 86-18059884797

[Skype] sales@saulcontrol.com

VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

1 Year Warranty

1 Year Warranty